Home

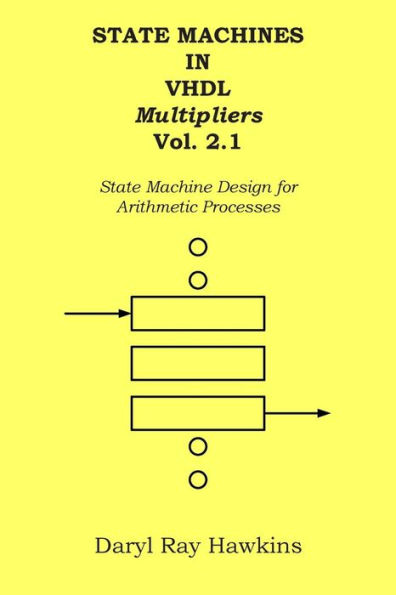

State Machines in VHDL Multipliers Vol. 2: State Machine Design for Arithmetic Processes

Barnes and Noble

State Machines in VHDL Multipliers Vol. 2: State Machine Design for Arithmetic Processes

Current price: $24.99

Barnes and Noble

State Machines in VHDL Multipliers Vol. 2: State Machine Design for Arithmetic Processes

Current price: $24.99

Size: OS

Loading Inventory...

*Product information may vary - to confirm product availability, pricing, shipping and return information please contact Barnes and Noble

This booklet contains all the information required to implement multiplier circuits in FPGA and ASIC devices as state machines. Four designs are provided ranging from simple to high performance with suggestions for even higher performance. Also included is a comprehensive chapter on normalizing and rounding, fixed-point as well as floating-point. The use of carry-save adders for partial product multiplication. Combining embedded array multipliers available in most FPGA devices for fashioning high perform large operand multipliers. Each design covered has a fully coded and fully functional design in VHDL as a state machine, with normalizing, rounding, and overflow included. Each design is also scalable in terms of operand size and the size of integer and fractional portions.